FPGA implementation of a template matching-based real-time spike sorter for extracellular multi-electrode recordings of neural signals

Filed under:

Electrophysiology

Jelena Dragas (ETH Zurich), David Jaeckel (ETH Zurich), Felix Franke (ETH Zurich), Andreas Hierlemann (ETH Zurich)

Signals in neural networks are propagated by means of short voltage pulses (spikes) of the cell membrane potential. Typically, extracellular electrodes sense spikes of several cells, which need to be correctly detected and assigned to the individual cells they originate from (referred to as sorting). Several factors render spike sorting error-prone: Low signal to noise ratio and simultaneous activity of different cells overlapping in the recordings. Moreover, the speed of sorting becomes crucial in applications where a feedback loop is employed to perform stimulation based on recorded cell activity.

This work describes an implementation and optimisation of a spike-sorting algorithm on a Field Programmable Gate Array (FPGA), targeting multi-electrode systems for extracellular neuronal recordings, where the activity of a single neuron is recorded on multiple electrodes. The algorithm relies on optimal linear filters (Franke‘11), matched to the prototypical multi-electrode spike waveforms (templates), where each neuron has one associated multi-electrode filter. Filter coefficients are calculated off-board, and are periodically loaded in the FPGA in order to adapt the filters to, e.g., changing spike templates caused by cell drift.

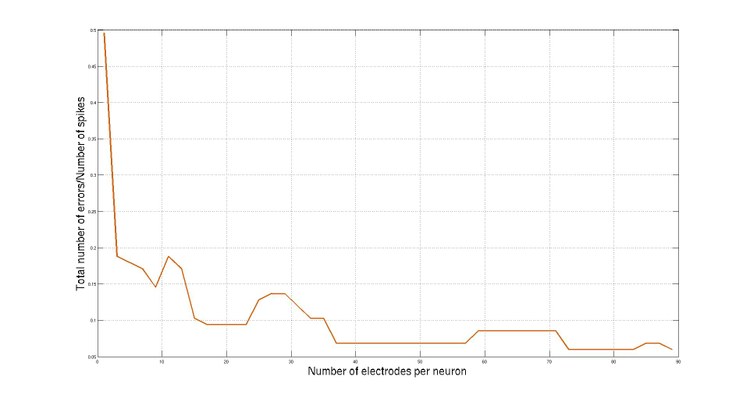

The performance of the real-time spike sorter has been assessed using simulations of mouse retinal ganglion cell recordings in a microelectrode array (MEA) system (Jaeckel‘12). Limited resources of an FPGA call for a trade-off between the number of electrodes per template and the sorting performance. For a simpler algorithm implementation, excluding overlap treatment, the latency of the sorting corresponds to half of the single electrode template length in addition to the algorithm overhead. In the above-mentioned data set, single electrode templates are 3ms long (sampled at 20kHz), and the algorithm overhead is 15 sampling cycles, resulting in a total latency of 2.25ms. The total number of errors (including false negatives and false positives), normalised to the expected number of spikes, is shown in Fig.1 as a function of the number of electrodes per neuron. It can be seen that even a small number of electrodes per neuron ensures a good sorting performance.

Low latency between spike occurrence and spike classification allows for real-time closed-loop stimulations with high spike-sorting performance. However, the spike sorter is not a stand-alone module and pre-processing needs to be done in order to obtain the filter coefficients.

This work describes an implementation and optimisation of a spike-sorting algorithm on a Field Programmable Gate Array (FPGA), targeting multi-electrode systems for extracellular neuronal recordings, where the activity of a single neuron is recorded on multiple electrodes. The algorithm relies on optimal linear filters (Franke‘11), matched to the prototypical multi-electrode spike waveforms (templates), where each neuron has one associated multi-electrode filter. Filter coefficients are calculated off-board, and are periodically loaded in the FPGA in order to adapt the filters to, e.g., changing spike templates caused by cell drift.

The performance of the real-time spike sorter has been assessed using simulations of mouse retinal ganglion cell recordings in a microelectrode array (MEA) system (Jaeckel‘12). Limited resources of an FPGA call for a trade-off between the number of electrodes per template and the sorting performance. For a simpler algorithm implementation, excluding overlap treatment, the latency of the sorting corresponds to half of the single electrode template length in addition to the algorithm overhead. In the above-mentioned data set, single electrode templates are 3ms long (sampled at 20kHz), and the algorithm overhead is 15 sampling cycles, resulting in a total latency of 2.25ms. The total number of errors (including false negatives and false positives), normalised to the expected number of spikes, is shown in Fig.1 as a function of the number of electrodes per neuron. It can be seen that even a small number of electrodes per neuron ensures a good sorting performance.

Low latency between spike occurrence and spike classification allows for real-time closed-loop stimulations with high spike-sorting performance. However, the spike sorter is not a stand-alone module and pre-processing needs to be done in order to obtain the filter coefficients.

Preferred presentation format:

Poster

Topic:

Electrophysiology

Latest news for Neuroinformatics 2011

Latest news for Neuroinformatics 2011 Follow INCF on Twitter

Follow INCF on Twitter